## A Small Dual Mixer Time Difference (DMTD) Clock Measuring System

W.J. Riley Hamilton Technical Services Beaufort, SC 29907 USA

#### Introduction

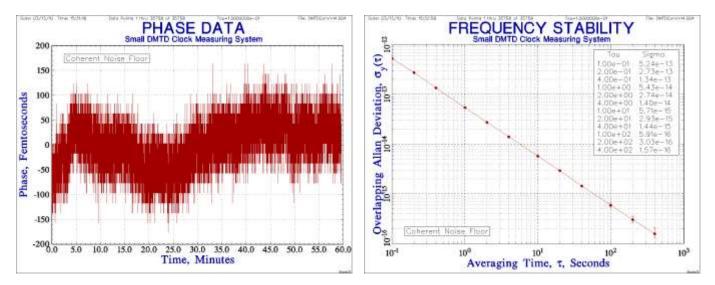

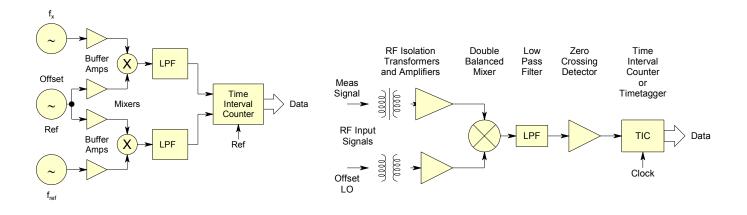

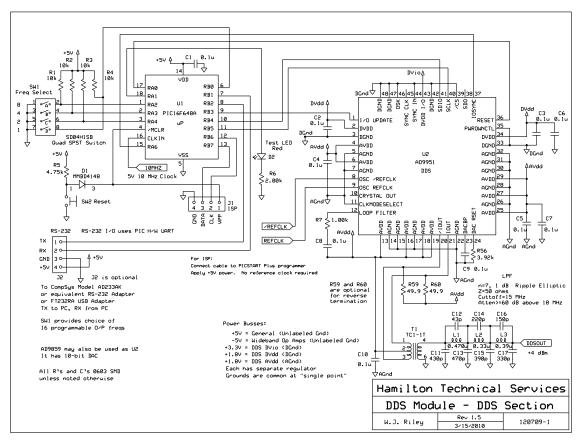

This paper describes a small and relatively simple Dual Mixer Time Difference (DMTD) clock measuring system (see Figure 1). A DMTD system is a well-established way to make high resolution phase measurements on precision frequency sources. This system is intended mainly for experimental purposes, but can be used to make low-noise measurements on up to three clocks versus a reference at the same nominal frequency in the range of 1-20 MHz. The system has a resolution of 20 femtoseconds for a 10 Hz beat frequency at an RF frequency of 10 MHz as shown in Figure 2. It has achieved a coherent noise floor below  $1 \times 10^{-13}$  at 1 second without phase averaging or cross-correlation, as shown in Figure 3, and well below that with cross-correlation. The design and implementation of the system hardware is described in detail. See Appendix I for a table of specifications for the Small DMTD Clock Measuring System.

Figure 1. The Small DMTD System

Figure 3. Small DMTD System Frequency Stability

#### • DMTD System Description

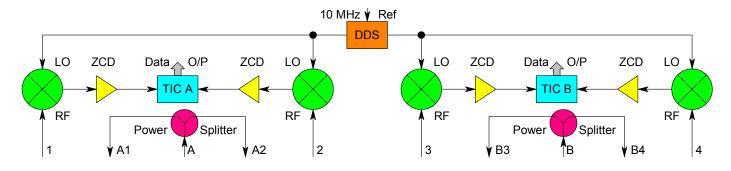

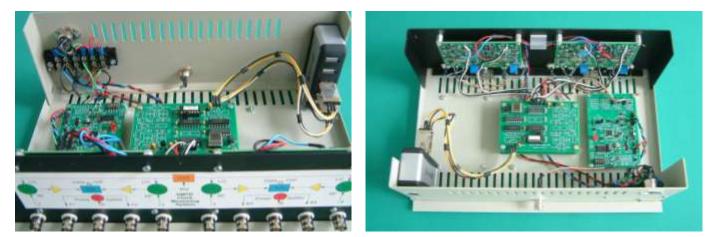

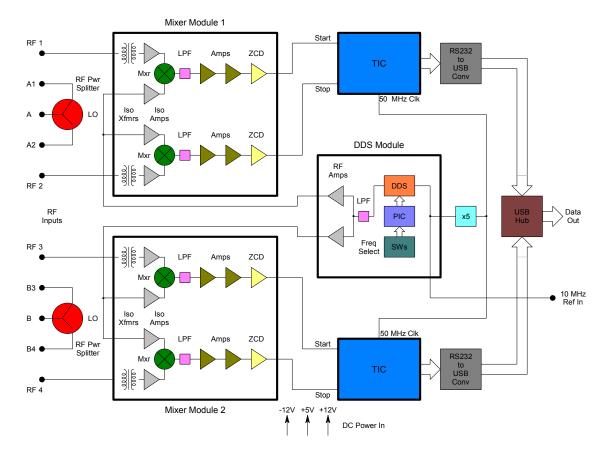

The system has two mixer modules, each with dual mixers having RF and offset LO inputs whose lowpassed outputs are amplified and processed by zero-crossing detectors to produce start and stop signals for two time interval counter modules. The offset LO signals are generated by a direct-digital synthesizer (DDS) module from a 10 MHz reference. The system also includes a pair of RF power splitters. This basic system, shown in the block diagram of Figure 4 and the photographs of Figure 5, can be configured in several ways to make coherent system noise tests, measurements on one or two pairs of clocks, and cross-correlation measurements on one pair of clocks. The system includes a Windows<sup>®</sup> PC program to capture data via a USB interface for subsequent analysis with Stable32.

Figure 4. Block Diagram of Small DMTD Clock Measuring System

| DMTD System    | Input Connections |               | Output             | Remarks                           |

|----------------|-------------------|---------------|--------------------|-----------------------------------|

| Configuration  | Section A         | Section B     | Usage              |                                   |

|                | A = Ref clock     | 3= Meas 2     | TIC $A = 1$ vs Ref | Two meas clocks measured against  |

| Standard       | 2 = Meas 1        | A2 to Input 3 | TIC $B = 2$ vs Ref | Ref clock using standard DMTD     |

|                | A1 to Input 1     | B splitter NC |                    | methodology.                      |

|                | A = Ref clock     | B=Meas Clock  | TIC $A = Ref$      | Ref and meas clocks compared      |

| Correlation    | A1 to Input 1     | B3 to Input 2 | TIC $B = Meas$     | with sections A and B. Cross      |

|                | A2 to Input 3     | B4 to Input 4 | Use Cross ADEV     | ADEV cancels uncorrelated noise.  |

|                | A = Source        | Optional      | TIC $A = System$   | Coherent inputs to measure system |

| Coherent A     | A1 to Input 1     |               | Noise              | noise. Section B can be used in   |

|                | A2 to Input 2     |               |                    | same way.                         |

|                | A = Source        | B = Source    | TIC $A = Meas 1$   | Coherent inputs from external     |

| Cross Coherent | A1 to Input 1     | B3 to Input 2 | TIC $B = Meas 2$   | splitter to measure cross         |

|                | A2 to Input       | B4 to Input 4 | Use Cross ADEV     | correlation system noise.         |

Figure 5. Photographs of the Small DMTD Clock Measuring System

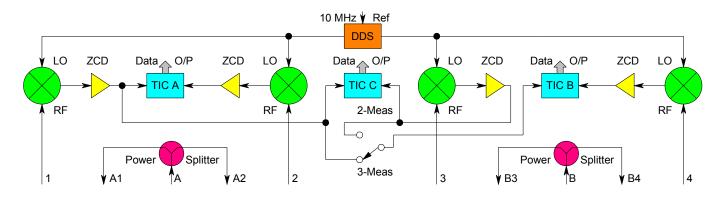

## • Expanded DMTD System

The basic DMTD clock measuring system may be expanded with a 3<sup>rd</sup> TIC whose start input is connected to the ZCD of mixer 1 and whose stop input is connected to the ZCD of mixer 3 as shown in Figure 6.

Figure 6. Expanded DMTD Clock Measuring System

In this arrangement, the 2-meas coherent configuration with separate A and B sources can use TIC C as an optional incoherent output. In the 3-meas arrangement with the TIC B start input also connected to the ZCD of mixer 1, the system can be used to measure three clocks against the Input 1 reference, a configuration well-suited for 3-cornered hat intercomparisons.

## • DMTD Clock Measuring Systems

A DMTD clock measuring system combines the heterodyne technique of resolution enhancement with a time interval counter to measure the relative phase of the beat signals from a pair of mixers driven from a common offset reference. It is one of the most precise ways to compare clocks all having the same nominal frequency. Its advantages include high resolution, low noise, phase data, no fixed reference channel and cancellation of offset reference noise and inaccuracy, while its disadvantages include complexity and operation at a single carrier frequency.

Figure 7. Block Diagrams of a DMTD Clock Measuring System

The DMTD system can be expanded to multiple channels by adding additional buffer amplifiers and mixers, and time tagging the zero-crossings of the beat notes for each channel, this arrangement allows any two of the clocks to be intercompared. The offset reference need not be coherent, nor must it have particularly low noise or high accuracy, because its effect cancels out in the overall measurement process. For best cancellation, the zero-crossings should be coincident or interpolated to a common epoch. Additional counters can be used to count the whole beat note cycles to eliminate their ambiguity, or the zero-crossings can simply be time tagged. The measuring system resolution is determined by the time interval counter or time tagging hardware, and the mixer heterodyne factor. For example, if two 5 MHz sources are mixed against a common 5 MHz - 10 Hz offset oscillator (providing a  $5 \times 10^6/10 = 5 \times 10^5$  heterodyne factor), and the beat note is timetagged with a resolution of 100 nsec (10 MHz clock), the measuring overall system resolution is  $10^{-7}/5 \times 10^5 = 0.2$  psec.

Multichannel DMTD clock measuring systems have been utilized by leading national and commercial metrology laboratories for a number of years [1-5, 18-20]. An early commercial version is described in Reference [3], a newer technique is described in Reference [8], and the Timing Solutions Corporation TS-3020 is an example of such a system [6]. The Stable32 software [11] has capabilities for reading the data files created by a TS-3020 system, allowing clock records to be conveniently processed.

The RF signals are isolated by RF transformers to avoid ground loops, and by isolation amplifiers to provide good input cable termination and reverse isolation for mixer products. It is important that those components have low phase sensitivity to temperature variations. The mixer is followed by a low pass filter to separate the audio beat signal from the RF components. The most critical component is the zero crossing detector or comparator that converts the analog beat signal into a digital waveform. It must have low noise and offset, and high speed so that the relatively slow beat signal is converted to a fast switching signal with low jitter at its exact zero crossing, and without crosstalk between adjacent channels [16].

The zero crossing detector output becomes one input of a time interval counter, or is timetagged by a digitizer with respect to an external system clock. The former is most commonly used for a simple heterodyne system, while the latter is generally used in a multi-channel DMTD system. Because of the large heterodyne factor that is normally used (e.g.,  $10^6$  for a 10 Hz beat note with 10 MHz signals), high measurement resolution does not require particularly fast time measurements (e.g., 0.1 psec overall resolution for a 10 MHz clock).

It is important to understand the potential vulnerability of a clock data acquisition system to interfering signals such as power line ripple. Signals at frequencies higher than one-half the sampling rate (e.g. 5 Hz for a 10 Hz beat note) are aliased and appear in the data as interference at lower frequencies. The system does not, and, as a practical matter, cannot have, low pass filtration to avoid such aliasing. Hence the importance of the RF isolation transformers and other precautions to avoid contamination by interfering signals. One should be alert to strange results, such as oscillations in an Allan deviation plot, which can be a sign of an aliasing problem. A higher beat frequency and sampling rate, perhaps followed by digital low pass filtration and decimation, is another way to reduce those problems, at the expense of lower resolution or the need for a higher performance time digitizer. Satisfactory results are usually obtained, as long as one remains aware of the possibility of aliasing difficulties.

#### The Small DMTD Clock Measuring System

Figure 8. Block Diagram of the Small DMTD Clock Measuring System

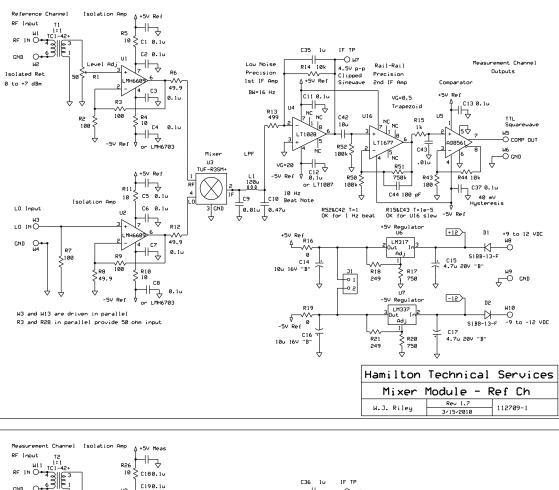

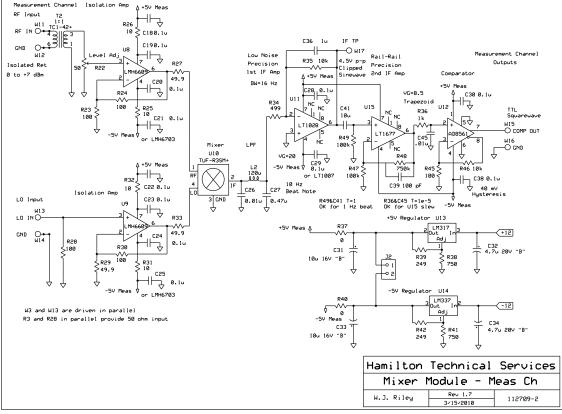

### Mixer Module

The mixer module of the Small DMTD system follows the general approach described in Reference 16 and 23, with a signal path that progresses from a low noise narrow bandwidth low slew rate input stage to a fast output stage zero crossing detector. Its distinguishing features are AC coupling to suppress the DC offset TC of the mixer diodes and the use of a high speed comparator as the last stage.

Figure 9. Mixer Module Schematic

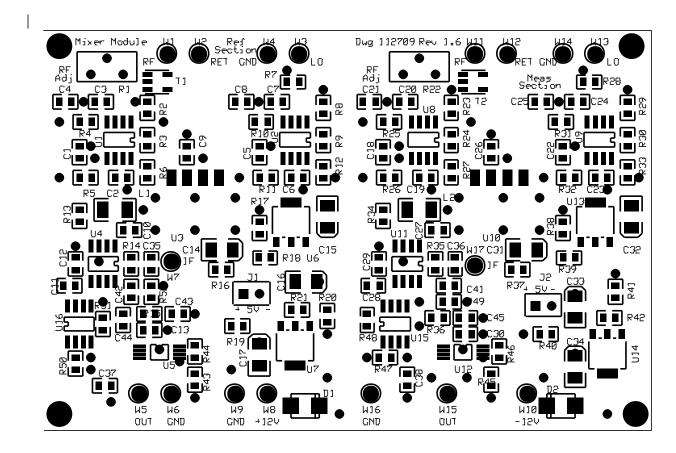

The circuit schematic and board layout of the experimental Small DMTD Mixer Module are shown in Figures 9 and 10.

Figure 10. Mixer Module Board Layout

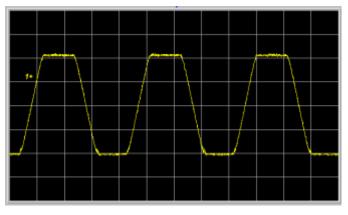

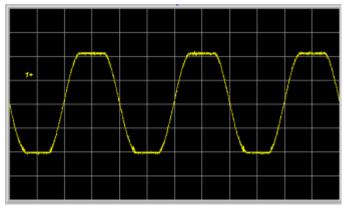

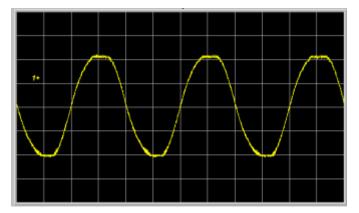

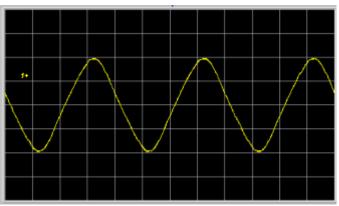

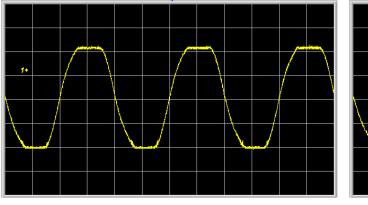

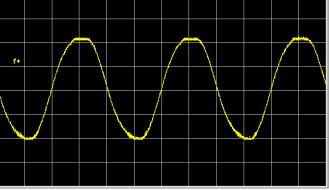

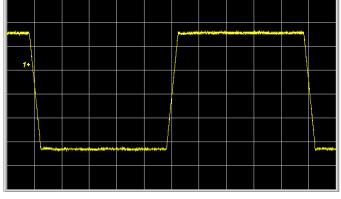

The waveforms at the IF test point at the output of the first IF amplifier are shown in Figure 11 for beat frequencies of 1, 5, 10 and 100 Hz with an RF input level of +3 dBm, the RF level adjustment set to maximum, and a first IF amplifier voltage gain of 20 and a bandwidth of 16 Hz. Figure 12 shows the IF test point waveforms at 10 Hz at RF inputs of 0 and +7 dBm, and Figure 13 shows the waveforms at the output of the IF amplifier (the input to the comparator) at those RF levels.

f=1 Hz , X=250 ms/div, Y=2 V/div, S=36 V/s

f=5 Hz , X=50 ms/div, Y= 2 V/div, S=160 V/s

f=10 Hz , X=25 ms/div, Y=2 V/div, S=320 V/s f=100 Hz , X=2.5 ms/div, Y=0.5 V/div, S=530 V/s Figure 11. IF Test Point Waveforms at RF=+3 dBm, IF Gain=Max, VG=20, BW=16 Hz

RF = +7 dBm, X = 25 ms/div, Y = 2 V/div Figure 12. IF Test Point Waveforms at f=10 Hz, IF Gain=Max, VG=20, BW=16 Hz

### • Time Interval Counter Module

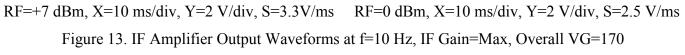

The Small DMTD system uses a version of the PICTIC time interval counter designed by Richard McCorkle [21]. In particular, this application uses a 50 MHz clock prescaler PICTIC without an analog interpolator and with a higher serial communications rate. A block diagram of this PICTIC is shown in Figure 14. Detailed design, schematic, parts list, board layout and assembly code information for the PICTIC is available in Reference 21.

Figure 14. Block Diagram of PICTIC Time Interval Counter

Several approaches were investigated for the 50 MHz PICTIC clock source, including free-running 50 MHz XOs, 100 MHz OCXOs divided to 50 MHz, a phase-locked 100 MHz OCVCXO divided to 50 MHzs and a x5 harmonic multiplier from 10 MHz, the latter chosen as the most practical coherent choice. Inaccuracy of the TIC clock affects the measurement scale factor, deleveraged by the system heterodyne factor.

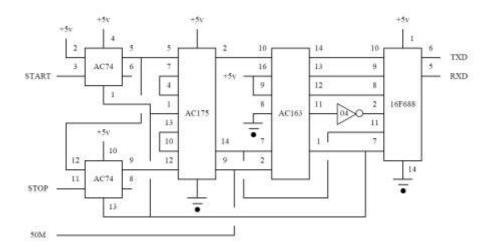

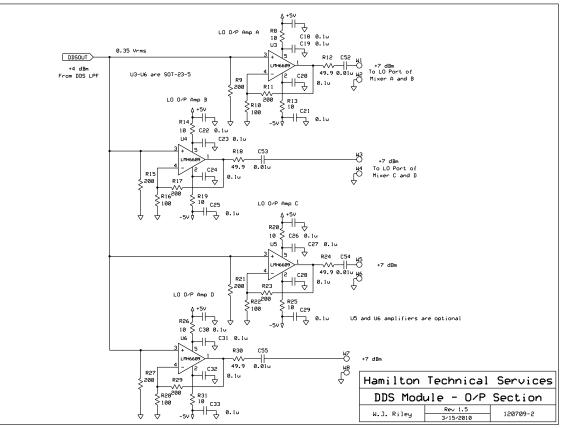

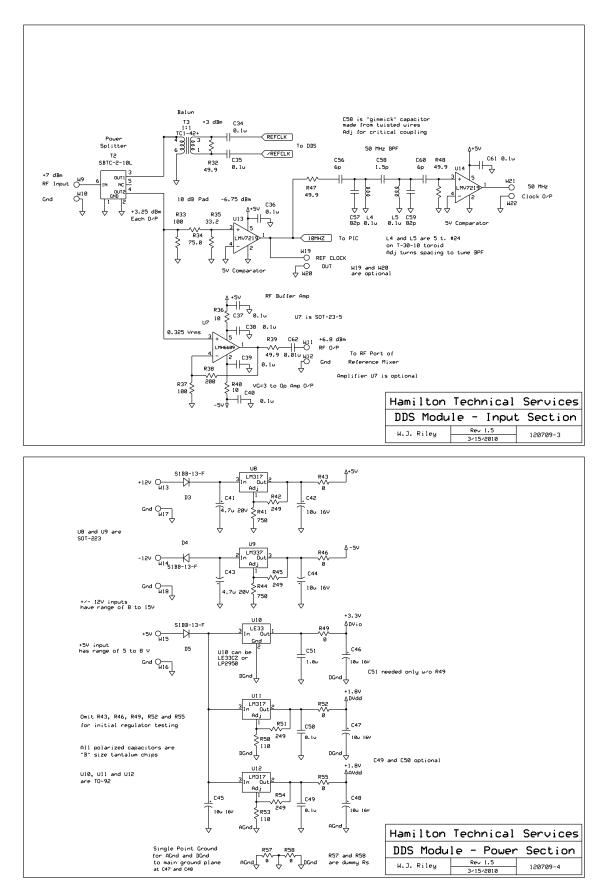

## • DDS Module

The DDS module provides the offset LO signal for the Small DMTD clock measuring system. It comprises ...

A schematic diagram for this module is shown in Figure 15. This schematic incorporates the changes made during evaluation of the first experimental version, including the addition of a x5 TIC clock multiplier. Only two of the four O/P amplifiers are required, and the 10 MHz reference O/P amplifier is also not required.

Figure 15. DDS Module Schematic

The DDS module is pre-programmed with 16 frequency settings selectable via an on-board DIP switch, as shown in Table 2. These choices provide frequency offsets of 1, 5, 10 and 100 Hz for four RF frequencies associated with GPS satellite atomic clocks.

| Table 2. Standard Offset LO DDS Settings |        |              |             |          |                               |  |

|------------------------------------------|--------|--------------|-------------|----------|-------------------------------|--|

| Switch Setting                           |        | RF Frequency | Freq Offset | DDS Word | DMTD Resolution, $\Delta f/f$ |  |

| Decimal                                  | Binary | MHz          | Hz          | Hex      | For 50 MHz TIC Clock          |  |

| 00                                       | 0000   | 5            | 1           | 0AAAAACE | 4.000000e-15                  |  |

| 01                                       | 0001   |              | 5           | 0AAAAB5D | 2.000000e-14                  |  |

| 02                                       | 0010   |              | 10          | 0AAAAC10 | 4.000000e-14                  |  |

| 03                                       | 0011   |              | 100         | 0AAAB8A5 | 4.000000e-13                  |  |

| 04                                       | 0100   | 10           | 1           | 15555579 | 2.000000e-15                  |  |

| 05                                       | 0101   |              | 5           | 15555608 | 1.000000e-14                  |  |

| 06                                       | 0110   |              | 10          | 155556BB | 2.000000e-14                  |  |

| 07                                       | 0111   |              | 100         | 15556350 | 2.000000e-13                  |  |

| 08                                       | 1000   | 10.23        | 1           | 15D2F1CD | 1.955034e-15                  |  |

| 09                                       | 1001   |              | 5           | 15D2F25C | 9.775171e-15                  |  |

| 10                                       | 1010   |              | 10          | 15D2F30F | 1.955034e-14                  |  |

| 11                                       | 1011   |              | 100         | 15D2FFA5 | 1.955034e-13                  |  |

| 12                                       | 1100   | 13.40134393  | 1           | 1C96EBD2 | 1.492388e-15                  |  |

| 13                                       | 1101   |              | 5           | 1C96EC61 | 7.461938e-15                  |  |

| 14                                       | 1110   |              | 10          | 1C96ED14 | 1.492388e-14                  |  |

| 15                                       | 1111   |              | 100         | 1C96F9A9 | 1.492388e-13                  |  |

Other frequencies can be substituted in the DDS module PIC firmware, and it has provisions (currently unimplemented) to enter frequency settings via a user interface through the same USB hub as used for the clock data. As presently configured with a 16 Hz IF bandwidth, the 100 Hz beat frequency is not well-supported, nor does the DMTDComm program work at that rate with its plotting features, although the raw DMTD data stream can be captured with Windows HyperTerminal for subsequent scaling and processing. Similarly, the IF bandwidth is unnecessarily wide, and the 0.16 Hz AC coupling in the IF amplifier is not ideal, for a 1 Hz beat frequency.

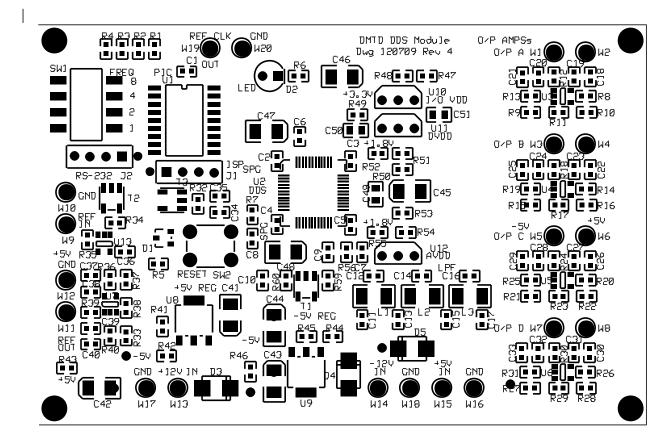

The board layout of the experimental Small DMTD DDS Module is shown in Figure 16.

Figure 16. DDS Module Board Layout

## LO Distribution

The DDS module has provisions for four isolated 50  $\Omega$  outputs to drive the LO inputs of the two dual mixer module via separate coaxial cables, but, to maintain best coherency, a single DDS output is used for each mixer module. The two LO inputs of each mixer module have paralleled 100  $\Omega$  termination resistors connected with a short length of  $\approx 100 \Omega$  twisted pair.

## • TIC Clock

The 50 MHz time interval counter clock should be coherent with the offset LO reference to avoid beats and other interference effects. That is accomplished from the 10 MHz reference squarewave by a passive x5 harmonic multiplier implemented by a 2-pole bandpass filter and high-speed comparator. Experiments conducted with a PIC clock derived from a free-running 100 MHz OCVCXO showed unexpectedly large (>  $pp10^{10}$ ) fluctuations as the oscillator was tuned slightly away from zero-beat that were dependent on grounding and lead dress. It is convenient to provide a switch to turn off and on the TIP clock as a way to start and stop the measurements on all channels simultaneously.

## • USB Data Interface

Data from the two TICs (three for an expanded system) are converted from TTL RS-232 to USB format by FTDI FT232R chips and combined in a USB hub inside the Small DMTD box. The same method can be used to communicate with the optional DDS module user interface. At the PC end, the USB connection is treated as a virtual COM port. The system uses 57600 baud, the highest rate supportable by the PICTIC processor.

Although TIC data is taken simultaneously for two coherent RF channels, these data are transferred via the serial USB interface sequentially and therefore obtain slightly different timetags. That difference is simply ignored for the case of the two data sets of a cross-correlation measurement.

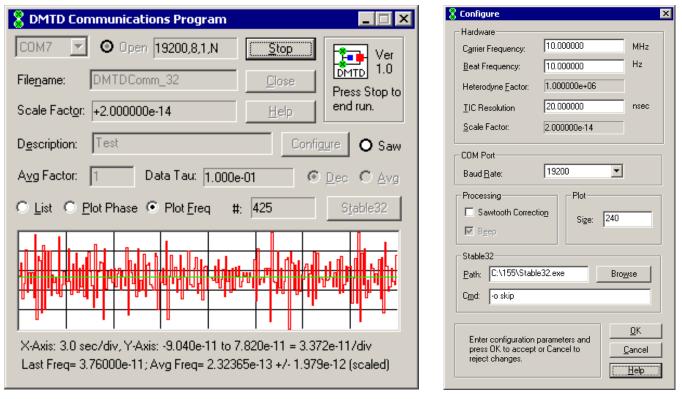

## DMTDComm Software

Operation of the Small DMTD clock measuring system is supported by the DMTDComm PC program that runs under Microsoft Windows<sup>®</sup>. This program configures and controls the Small DMTD system, displays the data stream as a list or plot of the phase or frequency, and captures the data to a disk file for analysis by Stable32. Multiple instances of DMTDComm can be launched to handle several Small DMTD measurement sections. The DMTDComm Main and Configure screens are shown in Figures 17 and 18 respectively.

Figure 17. DMTD Main Screen

Figure 18. DMTD Configure Screen

The phase and frequency plots and their annotations provide immediate feedback about the measurement results. The former can be used to assist in adjusting the relative phase of the RF inputs. During a cross-correlation coherent test, the latter plot for two sections will be highly correlated.

#### Data File Format

The DMTDComm program writes a Stable32compatible data file, as shown in the example of Figure 19. The file header includes lines indicating the Small DMTD system and the measurement tau. The first column is the MJD (derived from the local PC clock) when the data was written to the file (with a resolution of about 0.86 ms), and the second column is the phase reading in seconds (with a resolution exceeding that of the PICTIC).

```

Small DMTD Clock Measuring SystemLeft SectionTau: 1.000e-01MJDPhase, seconds55267.549286001.412200000000000e-1055267.549287151.412400000000000e-1055267.549288191.41180000000000e-1055267.549289361.41220000000000e-1055267.549290641.41240000000000e-1055267.549291791.41140000000000e-10

```

#### Figure 19. DMTDComm Data Format

#### Decimation and Averaging

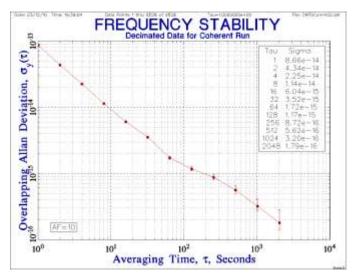

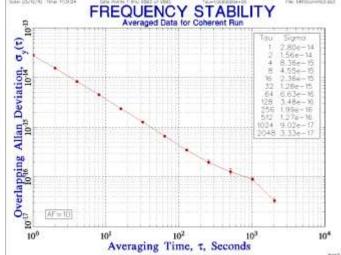

The DMTDComm program supports phase decimation and averaging. Decimation simply discards every nth phase data point. It is equivalent to frequency averaging, and is appropriate to reduce the amount of data when information at the shorter tau is not required. Phase averaging also reduces the size of the data file at the expense of losing information at shorter tau, but it also reduces the noise and changes the statistical properties of the data. Phase averaging is therefore seldom done and, if done, must be used with caution. Stability plots of decimated and averaged phase data from two portions of the same coherent run are shown in Figures 20 and 21. Both data sets have flicker PM noise with  $\alpha \approx +1.2$  at  $\tau =1$  second but the ADEV for the averaged data is x3.0 ( $\approx \sqrt{10}$ ) lower.

Figure 20. Stability Plot of Decimated Phase Data

Figure 21. Stability Plot of Averaged Phase Data

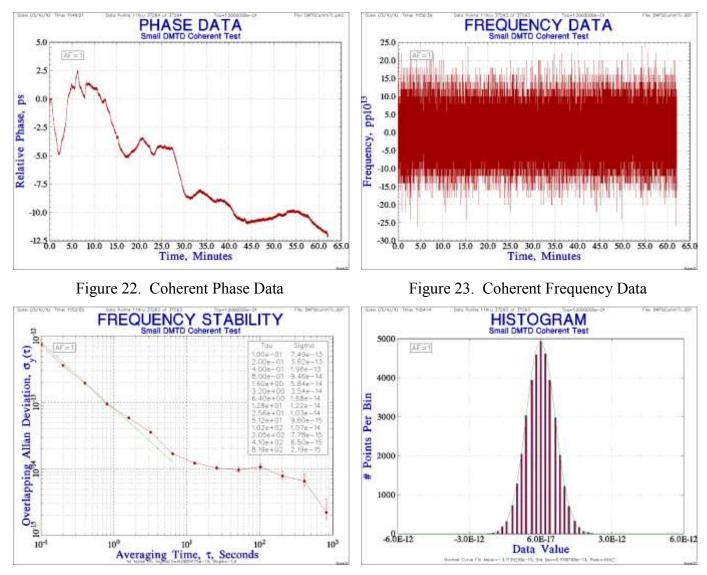

#### • Coherent Noise Floor

The noise floor of the Small DMTD system can be measured by applying the same source coherently to both RF inputs of a DMTD section. This can be done most easily by means of an internal RF power splitter. An example of a coherent noise floor test is shown in Figures 22-25 below.

Figure 25. Histogram of Frequency Data

The 1-second Small DMTD coherent noise floor is about x100 lower than the noise of the rubidium oscillator used as the common source (say  $1 \times 10^{-11}$  at 1-second), and is most likely limited by the degree of coherence rather than the noise of the measuring system. The most important factor determining the noise floor appears to be the relative delay between the two RF inputs rather than any aspect of the measuring system itself. When this phase difference is large, cancellation of the RF source noise is poor and one sees white FM noise at a higher level than when the phase difference is small and one sees a lower level of white PM noise for the DMTD system.

Coherent tests can be done at the other standard RF frequencies of 5, 10.23 and 13.40134393 MHz by using a high-resolution DDS at both RF inputs. But when a coherently-referenced DDS was used at 10 MHz as one of the RF inputs, it was found that the noise level was an order-of-magnitude higher even if its relative phase was adjusted close to zero, perhaps because of its internal clock multiplier.

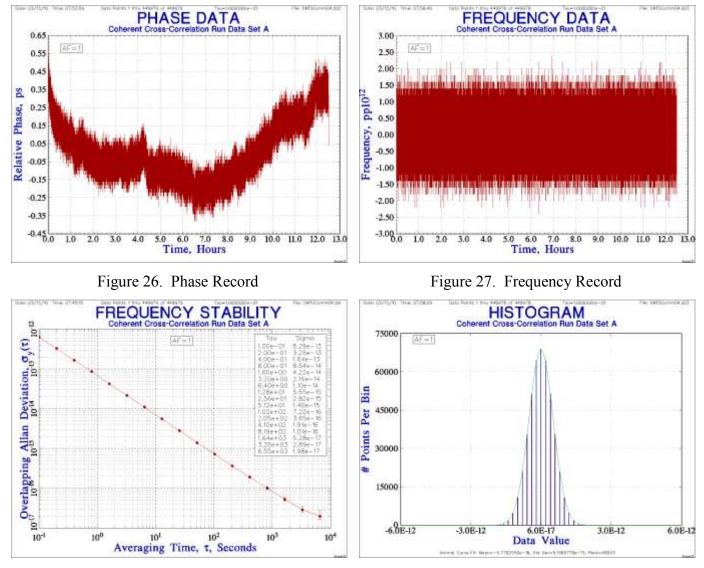

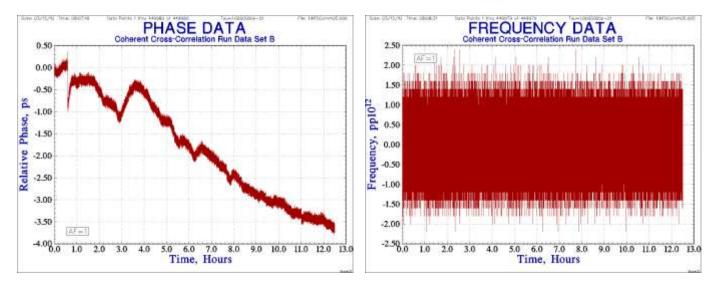

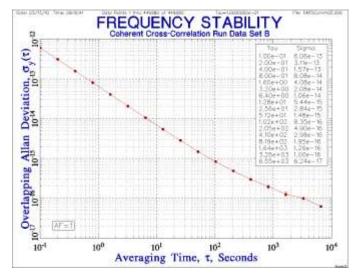

#### Coherent Cross-Correlation Noise Floor

The coherent cross-correlation noise floor can be measured by taking simultaneous coherent data with DMTD sections, starting and stopping the measurements with a TIC clock switch. Results of a longer coherent cross-correlation run are shown in Figures 26-34 below. The nominal phase difference of each section was adjusted to a small value of  $\approx 0.2$  ns for good source noise cancellation. The measuring system noise had a  $\alpha \approx +1.5$  at  $\tau = 0.1$  second, between white and flicker PM. The 2x10<sup>-14</sup>/second quantization level is visible in both the phase and frequency data plots, and most clearly in the frequency histograms, which are normally-distributed.

Figure 28. Frequency Stability

Figure 29. Frequency Histogram

Figure 30. Phase Record

Figure 32. Frequency Stability

Figure 34. Cross-Correlation Frequency Stability

Figure 33. Frequency Histogram

These data produced a 1-second cross-correlation ADEV of about  $6.0 \times 10^{-15}$ , as shown in the #ADEV stability plot of Figure 34. Compared with the individual 1-second stabilities of about  $6.5 \times 10^{-14}$ , the cross-correlation technique improved the noise floor by a factor of about x10.

#### LO Offsets

The standard Small DMTD LO frequency offset options are 1, 5, 10 and 100 Hz, providing resolutions of 2e-15/s, 1e-14/s, 2e-14/s and 2e-13/s and measurement intervals ( $\tau$ 's) of 1, 0.2, 0.1 and 0.01 seconds respectively for a 50 MHz TIC clock. These resolutions can be observed in a plot or histogram of the measured frequency data.

#### Data Averaging

The DMTDComm program includes provisions for averaging the data as it is captured, either arithmetically (frequency averaging) or decimation (phase averaging). The latter reduces the noise but also changes the statistical properties of the data. Either method reduces the size of the data file.

#### Phase Spillovers

Phase spillovers in the TIC reading occur at increments of the RF carrier period (e.g., 100 ns for 10 MHz), and can be a problem when there is a significant frequency offset (e.g., a frequency offset of  $\Delta f/f = 1 \times 10^{-9}$  at 10 MHz results in a spillover every 100 seconds). The actual span of the TIC is larger by the heterodyne factor, of course (100 ms for a 10 Hz beat frequency). One solution for a stable source is to use a DDS as the RF reference, but a better solution is to replace the time interval counter with a time tagger and obtain the time interval as the difference between the measurement and reference channel time tags. The DMTDComm program is able to remove a reasonable number of phase spillovers from the data stream, resulting in a continuous phase record having a gap at each spillover. This "sawtooth correction" detects a phase change greater than half of full scale and adds or subtracts the known full scale amount from all subsequent readings. Because the exact spillover time is not known, a gap (zero value) is inserted in place of the reading at that point.

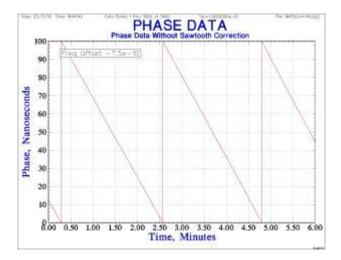

Figure 35. Phase Data w/o Sawtooth Correction

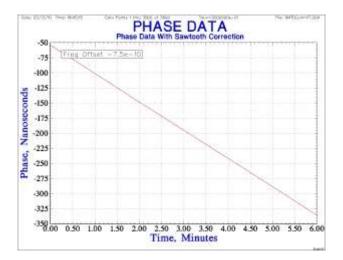

Figure 36. Phase Data with Sawtooth Correction

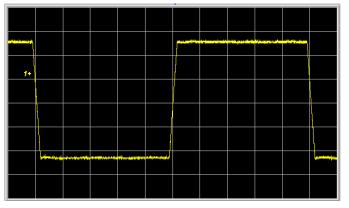

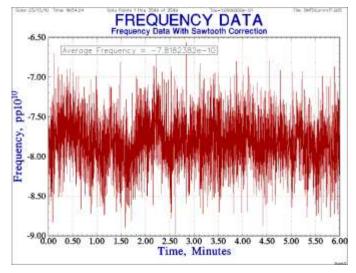

Figure 35. shows the uncorrected phase record for a small OCVCXO having a frequency offset of  $\approx$ -7.5x10<sup>-10</sup>. Phase spillovers occur with a period of about 100 ns/7.5e-10 = 133 s = 2.2 min. Figure 36 shows a later portion of the same run with the sawtooth correction activated, which produces a smooth phase record. The corresponding frequency record in Figure 37 shows no effect from the phase spillover.

Figure 37. Freq Data with Sawtooth Correction

## Crosstalk Effects

The most problematic crosstalk observed was between 10 MHz RF inputs and the 50 MHz PICTIC clock. That coupling can cause an aliased low frequency beat in the measured phase difference that depends on the exact TIC clock rate. A system with higher resolution would require better modular packaging, better shielding and perhaps optical isolation of the TIC start and stop signals.

### • Outliers

The Small DMTD data are reasonably outlier-free even at high data rates and over long observation times. Outliers that have values near the midpoint of the time interval counter do occur occasionally in the B section, and their cause is still under investigation.

## Sense and Accuracy

The sense and accuracy of the Small DMTD system was confirmed by applying a coherent input signal from a 48-bit DDS having a nominal  $+1\times10^{-11}$  frequency offset from 10 MHz. The #1 and #3 inputs correspond to the measurement channels of the A and B sections, producing positive-going phase ramps. The measured average frequency offsets agreed closely with the expected value.

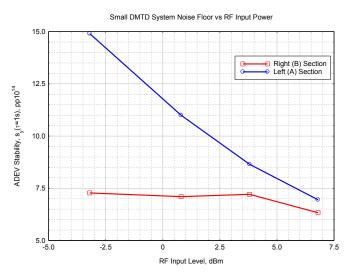

### • **RF Drive Level Sensitivity**

As expected, a lower RF drive level degrades the coherent noise floor, as shown in Figure 38. These evaluations were done with the right (A) section internal RF gain adjustment set with a nominal +7 dBm input for the largest ( $\approx 6.8 \text{ V p-p}$ ) undistorted sine wave IF signal after the first amplifier stage, giving a 0.25 V/ms slew rate at its zero crossings. The left (B) section gain set to maximum which produces a distorted  $\approx 8.3$  V p-p IF signal having a higher 0.40 V/ms slew rate. The distortion is produced in the mixer; the amplifier is not saturated. The corresponding slew rates of the trapezoidal second stage output at the comparator inputs are 2.0 and 4.0 V/ms. Clearly, the B section (red curve) is better as the RF drive level is reduced from its +7 dBm nominal.

Figure 38. Noise Floor vs. RF Input Power

### • Time Tagging

Time tagging would be better than time interval counting as the means for measuring the phase difference between the measurement and reference clocks, and is under consideration as an alternative to the PIC TIC in this design. The major advantages would be elimination of sawtooth phase spillovers and TIC the dead zone, and the ability to easily measure any channel against any other channel.

### • Thermal Considerations

Small, slow phase changes do not appreciably affect frequency stability results, so, if that is the measurement objective rather than phase per se, then normal laboratory temperature changes are not a serious problem. A major source of temperature sensitivity, phase offset in the mixer diodes, has been eliminated by AC coupling in the IF amplifier before the zero-crossing detector. No definitive phase versus temperature measurements have been made.

### • Mechanical Considerations

One picosecond corresponds to a distance of 0.3 mm in air, so a phase difference of 1e-13 second requires only 0.03 mm of mechanical displacement. This obviously means that all RF connections must be very rigid. No RF connectors are used inside the Small DMTD unit, but the external BNC connectors are subject to mechanical disturbance and must not be allowed to move during a measurement.

### • Measurement Example

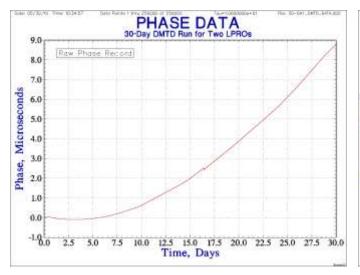

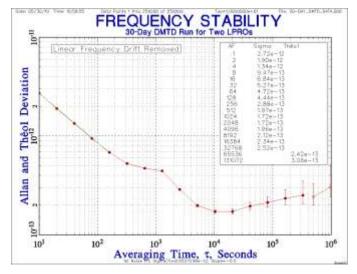

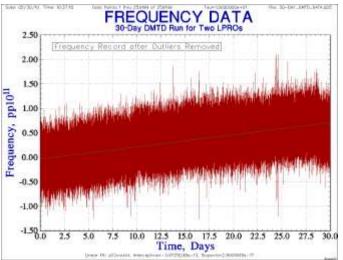

As an example of an actual measurement with the Small DMTD system, consider the comparison between two Datum LPRO commercial rubidium oscillators [26] for which  $\tau = 0.1$  second data were collected for one day, as shown in Figures 39-42..

Figure 41. Statistics

Figure 42. Frequency Stability

The measured short-term stability of these two rubidium oscillators,  $1.0 \times 10^{-11}$  at 1-second, is excellent, x2.5 better than their specification even without correction for two units. Also noteworthy is how close they are in average frequency, about  $2.5 \times 10^{-11}$ , without recalibration after their purchase on the surplus market. Their mutual frequency drift, although quite negligible for this short run, isn't particularly meaningful because one of the units was turned on a few hours before the run began.

A longer 30-day run was then conducted to better establish their "flicker floor" at the averaging time where the stability reaches its best value. The frequency of one of the units was adjusted close to zerobeat with respect to the other at the start of the run. The raw phase record, outlier-removed frequency record and drift-removed ThêoH stability plot for the run are shown in Figures 43-45. The phase record had one gross discontinuity caused by a power line transient during a thunderstorm. The relative frequency drift between these two mature rubidium oscillators was  $2.5 \times 10^{-13}$ /day. Their combined short-term white FM noise is an excellent  $\sigma_y(\tau)=8.6 \times 10^{-12}$ , their medium-term instability peaks in the 1000 second region, presumably due to temperature sensitivity and air conditioner cycling, and their long-term flicker FM noise floor is about  $2 \times 10^{-13}$ , a typical value for these devices.

Figure 43. Raw Phase Record

Figure 42. Drift-Removed Frequency Stability

### Conclusion

The Small DMTD system has satisfied its objective as a simple, high-resolution clock measuring instrument.

### • Acknowledgement

I wish to acknowledge the interest and kind assistance of Richard McCorkle with the PICTIC time interval counter used in this project.

### References

- 1. D.W. Allan, "Picosecond Time Difference Measurement System", Proc. 29th Annu. Symp. on Freq. Contrl., pp. 404-411, May 1975.

- 2. D.A. Howe, D.W. Allan and J.A. Barnes, "Properties of Signal Sources and Measurement Methods", Proc. 35th Annu. Symp. on Freq. Contrl., May 1981, pp. 1-47.

Figure 42. Outlier-Removed Frequency Record

- S.R. Stein, "<u>Frequency and Time Their Measurement and Characterization</u>", Chapter 12, pp.191-416, *Precision Frequency Control*, Vol. 2, Edited by E.A. Gerber and A. Ballato, Academic Press, New York, 1985, ISBN 0-12-280602-6.

- 4. S. Stein, D.Glaze, J. Levine, J. Gray, D. Hilliard, D. Howe and L Erb, "<u>Performance of an Automated High</u> <u>Accuracy Phase Measurement System</u>", *Proc. 36th Annu. Freq. Contrl. Symp.*, June 1982, pp. 314-320.

- 5. S.R. Stein and G.A. Gifford, <u>"Software for Two Automated Time Measurement Systems</u>", *Proc. 38th Annu. Freq. Contrl.* Symp, June 1984, pp. 483-486.

- Data Sheet, <u>Model 5110 Time Interval Analyzer</u>, <u>Timing Solutions Corporation</u> 5335 Sterling Dr, Suite B Boulder, CO 80301 USA.

- 7. Data Sheet, <u>A7 Frequency & Phase Comparator Measurment System</u>, <u>Quartzlock (UK) Ltd.</u>, Gothic, Plymouth Road, Totnes, Devon, TQ9 5LH England.

- 8. C.A. Greenhall, "Oscillator-Stability Analyzer Based on a Time-Tag Counter", *NASA Tech Briefs*, NPO-20749, May 2001, p. 48.

- 9. Gernot M.R. Winkler, "<u>Introduction to Robust Statistics and Data Filtering</u>", Tutorial at 1993 IEEE Freq. Contrl. Symp., Sessions 3D and 4D, June 1, 1993.

- 10. C.A. Greenhall, "<u>Frequency Stability Review</u>", Telecommunications and Data Acquisition Progress Report 42-88, Oct-Dec 1986, Jet Propulsion Laboratory, Pasadena, CA, pp. 200-212, Feb. 1987.

- Data Sheet, <u>Stable32 Software Package for Frequency Stability Analysis</u>, Hamilton Technical Services, Beaufort, SC 29907 USA.

- 12. Operations and Maintenance Manual, <u>TSC 5125A Phase Noise Test Set</u>, Timing Solutions Corporation, Boulder, CO 80301, Rev. G, May 16, 2006.

- C.A. Greenhall, "<u>Digital Signal Processing in the Radio Science Stability Analyzer</u>", TDA Progress Report 42-121, Jet Propulsion Laboratory, Pasadena, California, May 15, 1995.

- 14. See <u>http://www.go-mars.org</u>.

- 15. W.F. Walls, "Cross-Correlation Phase Noise Measurements", Proceedings of the 1992 IEEE Frequency Control Symposium, pp. 257-261, May 1992.

- 16. 1. G.J. Dick, P.F. Kuhnle, and R.L. Sydnor, "Zero Crossing Detector with Sub-Microsecond Jitter and Crosstalk", Proceedings of the 22<sup>nd</sup> Precise Time and Time Interval (PTTI) Applications and Planning Meeting , December 1990, pp. 269-282.

- 17. L. Galleani and P. Tavella, "Tracking Nonstationarities in Clock Noises Using the Dynamic Allan Variance", *Proc. 2005 Joint FCS/PTTI Meeting*, August 2005, pp. 392-396.

- L. Sojdr, J. Cermak, and R. Barillet, "<u>Optimization of Dual-Mixer Time-Difference Multiplier</u>", Institute of Radio Engineering and Electronics, Czech Academy of Sciences, Czech Republic, and Observatoire de Paris, Paris, France.

- L. Sojdr, J. Cermak, and G. Brida, "<u>Comparison of High-Precision Frequency Stability Measurement Systems</u>", *Proceedings of the Joint 2003 IEEE Frequency Control Symposium/17<sup>th</sup> EFTF Meeting*, May 2003, pp. 317-325.

- 20. C.A. Greenhall, A. Kirk, and R.L. Tjoelker, "<u>A Multi-Channel Stability Analyzer for frequency Standards in</u> <u>the Deep Space Network</u>", *Proceedings of the 38<sup>th</sup> Precise Time and Time Interval (PTTI) Applications and Planning Meeting*, December 2006, pp. 105-115.

- 21. R.H. McCorkle, "Simple PICTIC 250 ps Time Interval Counter".

- 22. S.R. Stein, "The Allan Variance Challenges and Opportunities", Proceedings of the Joint 2009 IEEE Frequency Control Symposium/ EFTF Meeting, April 2009, pp. 835-839.

- 23. O. Collins, "<u>The Design of Low Jitter Hard Limiters</u>", *IEEE Transactions on Communications*, Vol. 44, No. 5, May 1996, pp. 601-608.

- 24. FT232R USB UART IC, Document No. FT\_000053, Future Technology Devices International, 2009.

- 25. FT232RA Board, COMPSys, 2008.

- 26. LPRO Rubidium Oscillator, Datum, Inc., Irvine, CA, 2000.

# Appendix I

| Preliminary Specifications for<br>Small DMTD Clock Measuring System |                                        |                                      |  |  |  |  |

|---------------------------------------------------------------------|----------------------------------------|--------------------------------------|--|--|--|--|

| Parameter                                                           | Specification                          | Remarks                              |  |  |  |  |

| RF Frequency Range                                                  | 1-20 MHz                               | Can be extended in either direction  |  |  |  |  |

| RF Input Level                                                      | 0 to +7 dBm                            | Uncritical                           |  |  |  |  |

| RF Input Impedance                                                  | $50 \Omega$ nominal                    | Internally isolated                  |  |  |  |  |

| Standard RF Frequencies                                             | 5, 10, 10.23 and 13.40134393 MHz       | Can be changed via optional DDS      |  |  |  |  |

| Standard Beat Frequencies                                           | 1, 5, 10 and 100 Hz                    | Module user interface                |  |  |  |  |

| Measurement Tau                                                     | 1, 0.2, 0.1 and 0.01 second            | Determined by beat frequency         |  |  |  |  |

| # RF Channels                                                       | 2 pairs                                | 2 independent DMTD sections          |  |  |  |  |

| # Time Interval Counters                                            | 2                                      | Expandable to 3                      |  |  |  |  |

| # RF Power Splitters                                                | 2                                      | 2-way                                |  |  |  |  |

| DDS and TIC Reference                                               | 10 MHz                                 | Sets beat frequency and scale factor |  |  |  |  |

| Resolution                                                          | 20 femtoseconds                        | At 10 MHz with 10 Hz offset          |  |  |  |  |

| Noise Floor                                                         | ADEV $< 1 \times 10^{-13}$ at 1-second | W/O averaging or cross-correlation   |  |  |  |  |

| Measurement options                                                 | Phase decimation and averaging         | Using DMTDComm                       |  |  |  |  |

|                                                                     | Cross-correlation                      | Using Stable32                       |  |  |  |  |

| RF Connectors                                                       | BNC                                    | 4 RF, 6 splitter, 1 reference        |  |  |  |  |

| Controls                                                            | Run/Start clock toggle switch          | To start and stop all measurements   |  |  |  |  |

|                                                                     | Frequency select switch                | Internal 4-bit DIP switch            |  |  |  |  |

| Data Interface                                                      | USB 2.0 Virtual COM Port               | Stable32 compatible format           |  |  |  |  |

| Data Rate                                                           | 57600 Baud                             | 2 or 3 channels                      |  |  |  |  |

| Data Connector                                                      | USB Type B                             | Internal USB hub                     |  |  |  |  |

| Software                                                            | DMTDComm                               | Included (control and data capture)  |  |  |  |  |

|                                                                     | Stable32                               | Recommended (analysis)               |  |  |  |  |

| PC Compatibility                                                    | Microsoft Windows <sup>®</sup>         | Any 32-bit version                   |  |  |  |  |

| Size (L x W x H)                                                    | 8" x 12" x 4"                          | Excluding 4.5" x 3.0" x 2.5", 2.6 lb |  |  |  |  |

| Weight                                                              | 4.6 lbs                                | external power supply                |  |  |  |  |

| Power                                                               | 120 VAC, 60 Hz, TBD W                  | +5 VDC and ±12 VDC internal from     |  |  |  |  |

|                                                                     |                                        | external T512100/37 power supply     |  |  |  |  |

|                                                                     |                                        | with 5-pin DIN connector             |  |  |  |  |

| Availability                                                        | Not for sale                           | Contact Hamilton Technical Services  |  |  |  |  |

### **Appendix II**

### The Influence of Offset LO Noise and Nominal Phase Difference on the Small DMTD Noise Floor

### Introduction

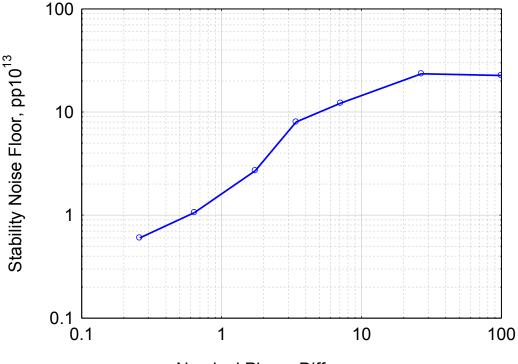

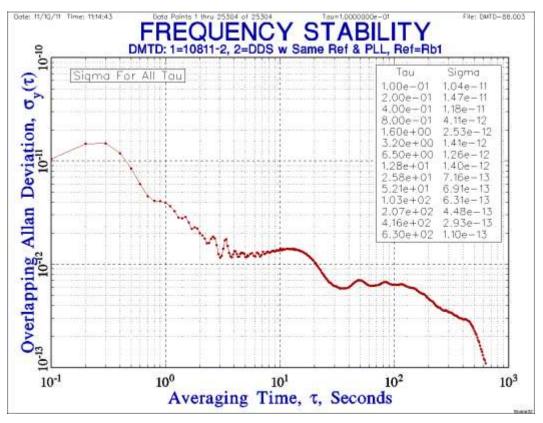

The noise floor of a DMTD clock measuring system depends on the noise of its offset local oscillator and the degree which that noise is cancelled [7, 8]. The former depends on the quality of the LO source while the latter is improved by minimizing the nominal phase difference between the start and stop signals from the two mixer channels. This appendix shows the dependence of the Small DMTD system noise floor on nominal phase difference for a DDS offset LO and an alternative offset crystal oscillator LO.

### • Effect of Nominal Phase Difference

The noise floor of the original Small DMTD system with its DDS offset LO is very sensitive to the phase difference between its two channels. Like many cancellation or nulling processes, the minimum noise occurs at a particular condition and degrades rapidly away from it. This is shown in Figure 1, where the nominal phase difference must be below about 1 ns to achieve a noise floor under  $1 \times 10^{-13}$  at 1 second, while, at the other extreme of large phase differences, the noise is more than an order-of-magnitude larger but less sensitive to the phase difference.

Nominal Phase Difference, ns

Figure 1. Small DMTD Noise Floor versus Nominal Phase Difference for DDS LO

## • Effect of LO Stability

The DMTD noise floor scales with the LO stability at the sampling time of the measuring system. This LO noise, typically white PM noise for a DDS offset LO synthesizer or flicker FM noise from an offset crystal oscillator, is reduced by the cancellation that occurs at small phase differences. Thus a lower noise LO source is particularly advantageous when a small phase difference cannot be maintained during the measurement.

Low noise ovenized crystal oscillators can provide stabilities between a few  $pp10^{12}$  and  $1pp10^{13}$  at the sampling times between 0.1 and 1 second used in a typical DMTD system. In contrast, a DDS synthesizer has somewhat poorer short term stability, but it offers coherency with an external reference. The autocorrelation function of the white FM VCXO noise extends to longer lags than does the white PM DDS noise.

### • DDS Noise

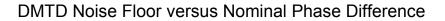

The measured noise of a DDS synthesizer similar to that used in the Small DMTD system is shown in Figure 2. These data were taken using the Small DMTD system with an HP 10811 OCVCXO as the common reference source which has a measured 1-second stability of about  $2x10^{-12}$ . The nominal phase difference was kept under 1 ns to minimize the system noise. The DDS synthesizer noise is about  $2x10^{-11}$  at 0.1 second and  $6x10^{-12}$  at 1 second.

Figure 2. Stability Plot for DDS Synthesizer

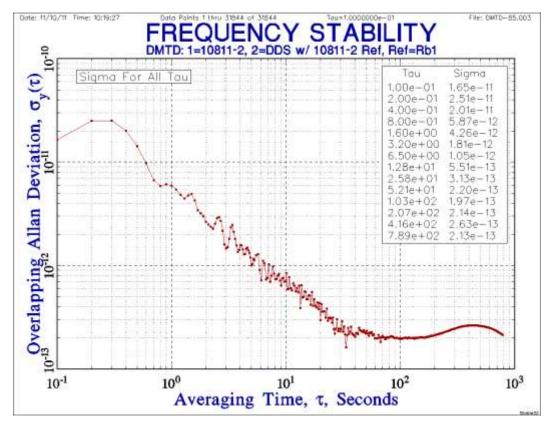

Another measurement was made using the same setup but with a fairly slow (0.2 second time constant) HP 10811 OCVCXO PLL cleanup loop after the DDS [9]. Those results, shown in Figure 3, show the improvement possible with that arrangement. The DDS synthesizer noise is about  $1 \times 10^{-11}$  at 0.1 second and  $4 \times 10^{-12}$  at 1 second. A slower PLL should be even better.

Figure 3. Stability Plot for DDS Synthesizer with OCVCXO PLL Cleanup Loop

Excluding its clock, the noise and spurious components of a DDS synthesizer can be attributed to three causes: (a) phase truncation, (b) quantization noise and (c) DAC non-linearity. Item (a) arises because the phase accumulator bits are truncated before accessing the sine lookup table, item (b) arises because of the finite bit size of the DAC, and item (c) is due to "glitches" and other analog defects. In general, all of these noise sources are correlated (i.e., coherent with the clock) and therefore not reducible by cross-correlation. In particular, the phase truncation spurs and quantization noise are highly deterministic and perfectly correlated. Additive thermal white and electronic flicker noise is normally much lower.

### • Cross-Correlation

A dual channel DMTD system using cross-correlation can lower the measuring system noise floor by cancelling the uncorrelated noise between the two channels. But this does not reduce the offset LO noise because it is common to the two channels. Nor would using two identical DDS synthesizers help because their noise would still be mostly coherent.

Using two DDS synthesizers with different clock multiplier factors and tuning words to produce (almost) the same offset frequency would seem likely to de-correlate their noise, and if their frequency difference is very small it would probably not be a problem. A pair of high-resolution 48-bit DDS would be needed. For example, for a +10 Hz offset at 10 MHz, 48-bit DDSs clocked at 10 MHz using clock multipliers of x11 and x12 would use hex tuning words of 1745D2FAD0B2 and 155556BB3F4D and have a fractional frequency difference with respect to 10 MHz of about  $3.553 \times 10^{-14}$ , about 3.07 ns per day.

But of those approaches require both more complicated hardware and processing and their effectiveness is uncertain.

Several authors have proposed and investigated schemes for reducing DDS noise by using an array of those devices in which their correlated carrier powers add while their uncorrelated noise and spurs do not and are therefore suppressed [1-6]. It is unclear, however, exactly why and to what degree the noise of two DDS synthesizers is uncorrelated. One such scheme applies different pseudo-random phase modulation signals to each DDS to insure noise de-correlation but this requires many elements to make an improvement.

Introducing a constant phase shift between two DDS synthesizers does tend to decorrelate their noise, and the sampling noise becoming uncorrelated when the phase difference is an odd multiple of 90° [4]. This carrier phase shift is not acceptable in an ordinary DMTD configuration unless it is removed afterwards, or by a quadrature I-Q type RF processor.

## PLL OCVCXO Cleanup Loop

It is possible to use a low-noise OCVCXO in a slow PLL to clean up the short-term stability of a DDS (albeit at a single nominal frequency). The OCVCXO must have good stability (e.g., a few pp10<sup>12</sup>) at the sampling time of the DMTD system (e.g., 0.1 second), and the PLL loop time constant must be an order-of-magnitude slower than that (e.g., 1 second). It must also have respectable thermal stability over averaging times at least as long as the loop time constant. A 1<sup>st</sup>-order PLL with minimal DC gain (only enough to produce the required control voltage) is suitable and easy to implement without large component values. Two such offset LO sources could support cross-correlation noise reduction because the noise of the two OCVCXOs would be uncorrelated. A candidate for a 10 MHz + or -10 Hz offset OCVCXO for that application is the Milliren 250 Series, a 2" x 2" x 1" plug-in device available with an SC-cut crystal and having  $2x10^{-12}$  short-term stability similar to the larger HP 10811. Otherwise, the cleanup PLL circuit would be similar to that of the HP 10811 10 MHz OCVCXO and PLL module used in the testing above.

## • Incoherent Offset OCVCXO

The offset LO does not necessarily have to be coherently referenced to a frequency standard. A freerunning low-noise OCVCXO can be used as the offset source in a multi-channel system where the resulting data for a pair of channels (e.g., UUT and reference) are differenced before analysis thus removing the effect of their common LO. That approach was used in the original Timing Solutions TSC 3020 clock measuring system. The main disadvantage is that at least two sources must be measured. Figure 4 shows the measured noise floor of the Small DMTD system with a free-running Milliren 250 Series OCVCXO offset LO. The noise floor is somewhat higher at small phase differences with the 10 MHz +10 Hz OCVCXO offset LO but is nearly an order-of-magnitude better at intermediate phase difference values and has less dependence of the nominal phase difference, remaining below  $1 \times 10^{-12}$  for all phase differences.

Figure 4. Small DMTD Noise Floor versus Nominal Phase Difference for OCVCXO Offset LO

## Coherent Offset OCVCXO Pair

A pair of offset OCVCXOs coherently phase locked in a slow PLL to the same DDS synthesizer would have not only relatively low noise but their noise would be uncorrelated and thus could be significantly reduced by using cross-correlation. That combination is potentially the best offset LO arrangement, especially one that has to work at large phase differences.

### • Conclusion

The coherent DDS offset LO is best when measuring highly-stable syntonized sources such as atomic frequency standards that can be adjusted for and can maintain a small nominal phase difference, while an incoherent OCVCXO offset LO is recommended for measuring sources that cannot maintain that condition.

## References

- 1. K. Lauritzen, *Correlation of Signals, Noise and Harmonics in Parallel Analog-to-Digital Converter Arrays*, Ph. D Thesis, University of Maryland, 2009.

- 2. T.M. Comberiate, *Phase Noise and Spur Reduction in an Array of Direct Digital Synthesizers*, M, Sci. Thesis, University of Illinois at Urbana-Champaign, 2010.

- 3. T. M. Comberiate, J. P. Van't Hof, L. B. Ruppalt, K. C. Lauritzen, and S. H. Talisa, "Phase Noise Model for an Array of Combined Sources Using Direct Digital Synthesis (DDS)", *Proceedings of the 40th Annual Precise Time and Time Interval (PTTI) Systems and Applications Meeting*, pp. 301-313, December 2008.

- 4. K. C. Lauritzen, S. H. Talisa, and M. Peckerar, "Impact of Decorrelation Techniques on Sampling Noise in Radio-Frequency Applications", IEEE Transactions of Instrumentation and Measurement, IM-59, No. 9, pp. 2272-2279, September 2010.

- 5. T. M. Comberiate, K. C. Lauritzen, L. B. Ruppalt, C.A. Lugo and S. H. Talisa, "Spur Correlation in an Array of Direct Digital Synthesizers", *Proceedings of the 42th Annual Precise Time and Time Interval (PTTI) Systems and Applications Meeting*, pp. 569-584, November 2010.

- 6. Y. Yang, J. Cai and L. Liu, "A Novel DDS Array Structure with Low Phase Noise and Spurs", *Proceedings of the 13<sup>th</sup> International Conference on Communications Technology*, pp. 302-306, September 2011.

- 7. C. A. Greenhall, "Common-Source Phase Noise of a Dual-Mixer Stability Analyzer", *TMO Progress Report 42-143*, Jet Propulsion Laboratory, Pasadena, California, USA, November 2000.

- 8. C.A. Greenhall, A. Kirk, and G.L. Stevens, "A Multichannel Dual-Mixer Stability Analyzer: Progress Report", *Proceedings of the 33<sup>th</sup> Precise Time and Time Interval (PTTI) Applications and Planning Meeting*, pp. 377-384, November 2001.

- 9. W.J. Riley, "A 10 MHz OCVCXO and PLL Module", November 2011 (unpublished).

File: A Small DMTD System.doc W.J. Riley Hamilton Technical Services May 30, 2010 Revision A: April 5, 2012